在工业通信设备设计中,以太网变压器和集成RJ45连接器的布局直接影响信号完整性、EMI性能及PoE稳定性。沃虎电子(VOOHU)基于行业规范(IEEE 802.3)以及相关技术指南,为工程师提供PCB关键布局策略。

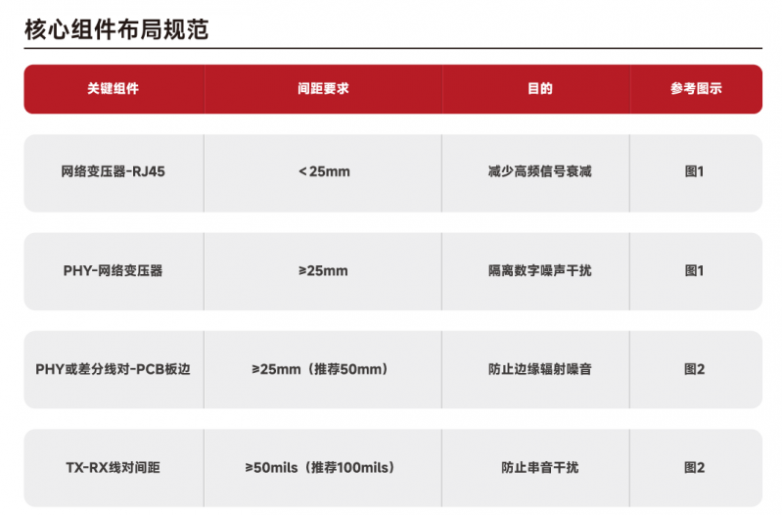

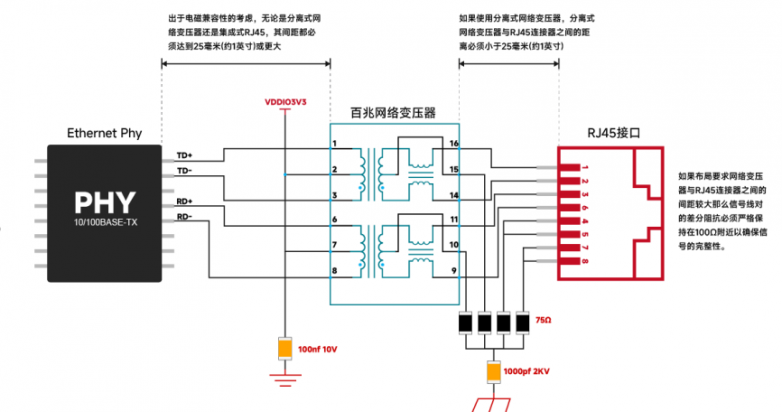

一、核心组件布局规范

二、走线长度与对称性

▪ 关键信号走线应尽量短,减少高频噪声影响(含电源/地平面噪声),并降低容性负载

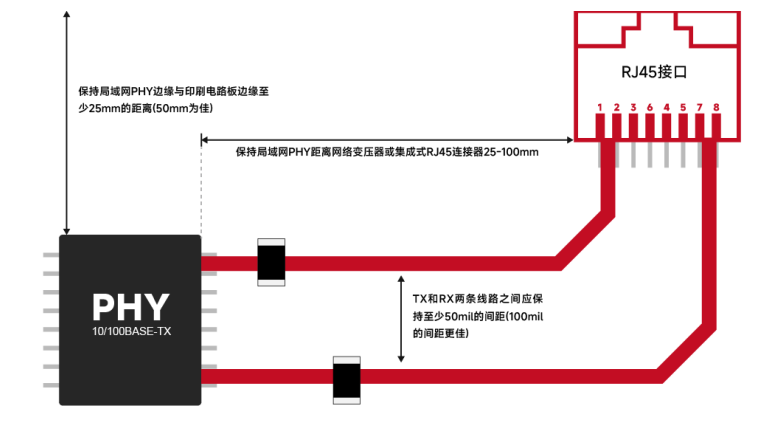

▪ 差分线对应尽量短且对称:从PHY芯片经网络变压器到连接器的总长应<4英寸

▪ 差分对内走线长度差应≤50mils(1.25毫米)且尽量对称。非对称/不等长走线会引发共模噪声

▪ 为减少线对间串扰,不同差分对间距需>50mils(1.25毫米)。此规则同样适用于板上其他收发器电路

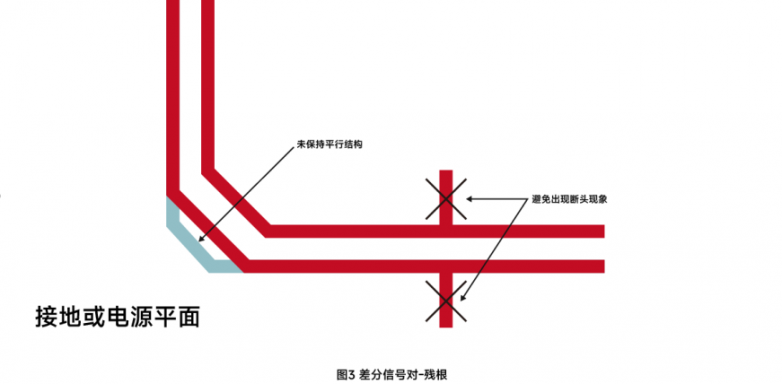

▪ 所有信号走线(尤其是差分对)应避免残桩,见图3

▪ 差分线对内部走线(如TD+与TD-)应平行且等长,以最小化延时差,降低共模噪声和EMI

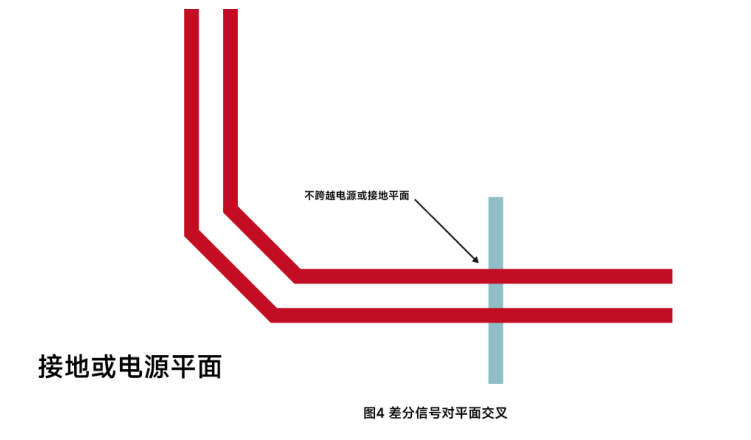

▪ 信号走线禁止跨越平面分割(图4)。跨越分割会导致回流路径异常,影响信号质量并引发EMI

▪ MDI信号走线需具有50Ω对地或100Ω差分受控阻抗

三、差分线对布线指南

为尽量减少高速信号布线区域内的串扰和传播延迟对电路板的影响,请遵循以下布线指南:

▪ 数字信号远离模拟走线(≥300mils/7.5毫米)

▪ 若其它层的数字信号无法用地平面隔离,应与差分对垂直布线

▪ 允许使用多口连接器模块,但各电路信号需严格隔离

▪ 差分线对内部最大间距≤10 mils

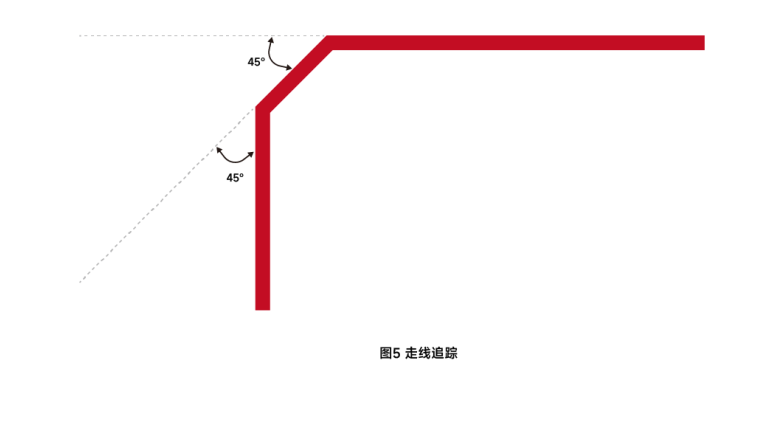

▪ 理想情况下信号路径无交叉或过孔。尽量同层布设整对走线。过孔导致阻抗突变需最小化(每个走线最多2个过孔)。高速信号需最小化拐角和过孔数量。90°弯折需用双45°替代(图5)

▪ 走线离板边距离需大于走线距地平面高度,使电场更易耦合至地平面

▪ 禁止在晶体/振荡器下方布线,防止时钟耦合。时钟驱动走线距开孔的最小距离需大于最大孔径尺寸

▪ 禁止在分割的参考平面上方布差分线对

▪ 差分线端接元件尽量靠近PHY芯片

四、走线几何结构

▪ 控制走线EMI辐射的关键:走线长度及线宽/距地高度比。为降低电感,高速信号和靠近地/电源层的信号层应尽量短而宽。理想宽高比为1:1至3:1。换层时若两层距电源/地距离不等,需调整线宽以保持阻抗

▪ 每对信号差分阻抗应为100Ω±15%。若工具无法设计差分走线,可设单端阻抗55-65Ω(前提是两走线间距最小化)。例如:层I上差分对宽8mils(0.2mm)、厚2mils(0.05mm)、间距8mils(0.2mm),FR4层厚8mils(ER=4.7)时,单端阻抗约61Ω,差分阻抗约100Ω

▪ 当差分对内部走线间距<30mils(边到边)时,需补偿边缘耦合效应(可能使差分阻抗降低达10Ω)

VOOHU是国内连接器厂商中的佼佼者,快捷的交期/一站式采购/技术支持/提供样/品专业成熟。您只需提出最终的应用需求及预算,VOOHU即可提供完整的一站式解决方案,为您的产品研发助力。

未经授权不得转载。发布者:阳信微生活,转转请注明出处:https://www.251800.com/5456.html